Verification through simulation

We can not only come up with the designs for your application…we also test your design for correct function and for correct timing with extensive simulation tools.

Functional simulations

We can execute functional simulations on the Register Transfer Level (RTL) for designs in VHDL. This simulation can also be executed independently of existing hardware or independently of hardware that does not yet exist. The only thing that is required is creating a testbench for the design. This simulation is possible to good advantage with ModelSim.

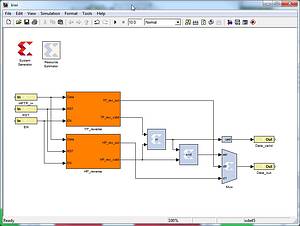

The function simulation of DSP algorithms and small designs done to good advantage on the basis of Matlab/Simulink. Thus for the development or input you can test whether the algorithms function on the target hardware with bit and cycle precision.

If the algorithms run on the PC as software, then after the simulation the block circuit diagram can automatically be converted in C-code.

This graphic programming has the following advantages

- Using function blocks clearly arranges the program and simplifies the documentation

- The function can be extensively tested

- If the pure software solution is too slow on the PC computer technology, then with modest effort a hardware supported FPGA-Design can be developed

Timing simulation

As with all FPGAs, the timing of complex designs can only be assessed with knowledge of the runtimes through the combiner logic and the connecting lines according to the place and route for the target hardware. Functional errors, induced by excessive run times, can be specifically located after this simulation. These errors can be resolved in an iterative process.

The essential results of the timing analysis are the slowest paths in the design, from which the maximum number of cycles can be determined. The design can also be evaluated through the ratio of logic runtime to the runtime of the connections.