Verifikation durch Simulation

Wir können das Design für Ihre Anwendung nicht nur entwerfen. Wir testen Ihr Design auch auf die korrekte Funktion und auf das richtige Timing mit umfangreichen Simulationswerkzeugen.

Funktionale Simulationen

Wir führen funktionale Simulationen auf Register Transfer Level (RTL) für Designs in VHDL durch. Diese Simulation kann auch unabhängig von vorhandener (oder noch nicht vorhandener) Hardware durchgeführt werden. Lediglich eine Erstellung der Testbench zum Design ist erforderlich. Mit ModelSim ist diese Simulation vorteilhaft möglich.

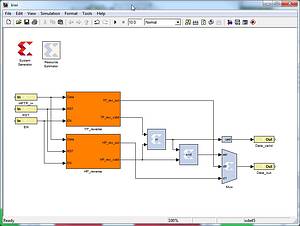

Die Funktionssimulation von DSP-Algorithmen und kleinen Designs ist auch sehr vorteilhaft auf der Basis von Matlab/Simulink möglich. So kann bei der Entwicklung bzw. Eingabe getestet werden, ob die Algorithmen bit-genau und zyklus-genau auf der Zielhardware funktionieren.

Sollen die Algorithmen als Software auf dem PC lauffähig sein, kann nach der Simulation das Blockschaltbild automatisch in C-Code umgewandelt werden.

Diese grafische Programmierung hat Vorteile

- durch Verwendung von Funktionsblöcken ist das Programm übersichtlich

- die Funktion kann ausgiebig simuliert werden

- sollte sich die reine Software-Lösung auf der PC-Rechentechnik als zu langsam erweisen, kann mit geringem Aufwand ein hardwareunterstütztes FPGA-Design entwickelt werden

Timing Simulation

Wie bei allen FPGAs kann das Timing umfangreicher Designs erst mit der Kenntnis der Laufzeiten durch die kombinatorische Logik und der Verbindungsleitungen nach dem Place & Route für die Zielhardware bewertet werden. Nach dieser Simulation können Funktionsfehler, hervorgerufen durch zu lange Laufzeiten, gezielt gefunden werden. In einem iterativen Prozess können diese Fehler behoben werden.

Eine Timing Analyse gibt grundsätzlich die langsamsten Pfade im Design an, woraus die maximale Frequenz ermittelt werden kann. Die Bewertung des Designs kann auch durch das Verhältnis von Logiklaufzeit zur Laufzeit der Verbindungen erfolgen.