# JPEG-Codec-IP-Core (Encoder) für FPGAs

### Anwendungen

- Digitalkameras und -camcorder

- Überwachungssysteme und -kameras

- ➤ Videokonferenzsysteme, smart cameras

- low-latency Kameras (geringste Verzögerungen)

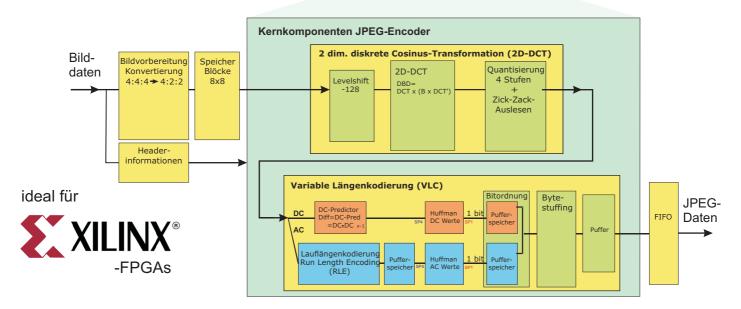

- JPEG-Kompression/Dekompression entsprechend "baseline process" nach CCITT T.81 (ISO/IEC 10918-1).

- Der JPEG-Codec besteht aus einem separaten Encoder- und Decoderteil, die einzeln oder parallel betrieben werden können. Hohe Leistungsfähigkeit und Robustheit im praktischen Einsatz.

- Geringste Verzögerungszeiten zwischen Dateneingang und komprimierten Datenausgang (2...8 µs).

- Dieser high-performance Codec ist für Einzelbilder hoher Qualität und/oder Motion-JPEG (MJPEG) geeignet.

- Geringer Platzverbrauch bei hoher Geschwindigkeit in XILINX FPGAs (Spartan-6 < 1200 Slices).

- Qualität und Komprimierung mit 4 oder mehr vorgegebenen oder benutzerdefinierten Quantisierungstabellen wählbar. Datenmenge des komprimierten Bildes liegt zwischen 1 % und 33 % der Datenmenge des unkomprimierten Bildes.

- Voller Reset vor und nach jedem Bild, d.h. bei Motion-JPEG hat jedes Bild gleiche Anfangsbedingungen.

- Leichtes Einfügen in ein vorhandenes HDL-Programm bzw. Verbinden mit Programmmodulen durch definierte Schnittstellen.

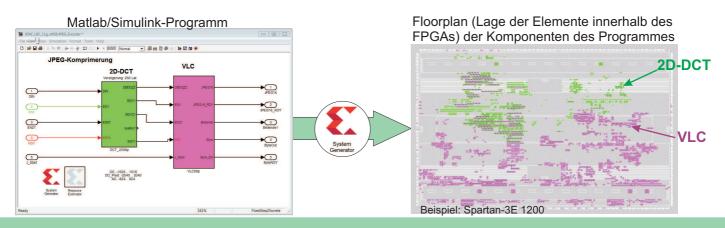

- Programmierung des gesamten JPEG-Codecs wurde mit grafischer Oberfläche (Matlab/Simulink mit XILINX System Generator) als modularer Aufbau ausgeführt.

- Bildgröße kann beliebig sein (z.B. 64 k x 64 k).

- Optionale Module für Videokamerasteuerung, Bayer-Pattern-Interpolation, Farbraumkonvertierung, RAM-Anbindung usw. sind verfügbar. Individuelle Anpassung der IP-Cores möglich.

- Optional mit automatischer Komprimierungssteuerung für limitierten Datendurchsatz (Datenmenge des komprimierten Bildes wird der Bandbreite der Schnittstelle effektiv angepaßt).

- Core für XILINX FPGAs einsetzbar (Spartan-3-Familie, Spartan-6, Virtex-4, Virtex-5, Virtex-6, 7-er Familie Artix, Kintex, Virtex, ZYNQ).

## Platzverbrauch und Geschwindigkeit

Der **JPEG-Encoder** (Kernkomponenten 2D-DCT und VLC) ist in den folgenden XILINX FPGAs mit dem Platzverbrauch nach Place & Route beispielhaft aufgelistet:

| FPGA       | Slice Reg | Slice<br>LUTs | Belegte<br>Slices | DSP48 oder<br>Emb. Mult. | BlockRAM | BlockRAM<br>/kbit |

|------------|-----------|---------------|-------------------|--------------------------|----------|-------------------|

| Spartan-3E | 2234      | 3442          | 2769              | 1                        | 5        | 80                |

| Spartan-6  | 2240      | 2790          | 1192              | 1                        | 3+2      | 56                |

| Virtex-5   | 2199      | 2818          | 1173              | 1                        | 1+3      | 80                |

| Virtex-6   | 2205      | 2653          | 1098              | 1                        | 1+3      | 80                |

| Virtex-7   | 2201      | 2640          | 1142              | 1                        | 1+3      | 80                |

| Kintex-7   | 2184      | 2591          | 1080              | 1                        | 1+3      | 80                |

Die möglichen maximalen Systemfrequenzen des Cores und die Verarbeitungsgeschwindigkeiten sind im Folgenden für FPGAs mit entsprechendem Speedgrade für den maximalen Systemtakt und maximalen Pixeltakt für den Encoder aufgelistet:

| FPGA       | Speedgrade | t <sub>max</sub> /ns | f <sub>System max</sub> /MHz | f <sub>Pixel max</sub> /MHz (24 bit/Pixel) |

|------------|------------|----------------------|------------------------------|--------------------------------------------|

| Spartan-3E | 4          | 8,3                  | 120                          | 60                                         |

| Spartan-6  | 2          | 5,68                 | 176                          | 88                                         |

| Spartan-6  | 3          | 4,81                 | 208                          | 104                                        |

| Virtex-5   | 2          | 4,17                 | 240                          | 120                                        |

| Virtex-6   | 2          | 3,12                 | 320                          | 160                                        |

| Virtex-7   | 2          | 3,29                 | 304                          | 152                                        |

| Kintex-7   | 2          | 3,67                 | 272                          | 136                                        |

Für hohe und höchste Qualitäten der komprimierten Bilder kann die Quantisierungstabelle und Geschwindigkeit angepaßt werden.

Unser Entwicklerteam steht auch für jede Anpassung und Hilfe bei diesem und anderen IP-Cores zur Verfügung.

# **Optionen**

- Headergenerierung und Bildvorbereitung

- Bildzeilenspeicher intern/extern mit Pixelsortierung (YYUV)

- > zusätzliche FIFOs für komprimierte Bilddaten

- ➤ Entwicklungsdienstleistungen rund um FPGA-Funktionen und -Applikationen

# **Bestellinfos**

JPEG-Enc-HQ JPEG-Encoder für Einzelbilder höchster Qualität

JPEG-Enc-Video JPEG-Encoder für Videostreams

JPEG-Enc-VV Vorverarbeitung der Bilddaten zum Encodereingang